## University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative **Exchange**

**Masters Theses** Graduate School

12-2007

# A 64-Channel Mixed-Signal Data Acquisition System for a Solid-State High Efficiency Neutron Detector Array

Anthony Gene Antonacci University of Tennessee - Knoxville

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Antonacci, Anthony Gene, "A 64-Channel Mixed-Signal Data Acquisition System for a Solid-State High Efficiency Neutron Detector Array. " Master's Thesis, University of Tennessee, 2007. https://trace.tennessee.edu/utk\_gradthes/107

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Anthony Gene Antonacci entitled "A 64-Channel Mixed-Signal Data Acquisition System for a Solid-State High Efficiency Neutron Detector Array." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Benjamin J. Blalock, Major Professor

We have read this thesis and recommend its acceptance:

Charles L. Britton, Jr., M. Nance Ericson

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a thesis written by Anthony Gene Antonacci entitled "A 64-Channel Mixed-Signal Data Acquisition System for a Solid-State High Efficiency Neutron Detector Array." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

| Benjamin J. Blalock |

|---------------------|

| Major Professor     |

| We have read this thesis and recommend its acceptance: |  |

|--------------------------------------------------------|--|

| Charles L. Britton, Jr.                                |  |

| M. Nance Ericson                                       |  |

Accepted for the Council:

Carolyn R. Hodges

Carolyn R. Hodges, Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# A 64-CHANNEL MIXED-SIGNAL DATA ACQUISITION SYSTEM FOR A SOLID-STATE HIGH EFFICIENCY NEUTRON DETECTOR ARRAY

A Thesis Presented for the

Master of Science Degree

The University of Tennessee, Knoxville

Anthony Gene Antonacci

December 2007

#### ACKNOWLEDGMENTS

I would first and foremost like to thank my committee Dr. Benjamin Blalock, Dr. Nance Ericson, and Dr. Chuck Britton for their valuable support throughout this project. Without their unmatched knowledge and experience in solid-state circuit design, this project would not have reached this level of success. Special thanks to Robert Greenwell for his support when submitting this ASIC to the MOSIS fabricator and during long testing hours in the lab. I would also like to thank James Vandersand for his help with the VHDL coding of this project. Thanks to Dr. Lloyd Clonts for assistance with the digital circuitry design and to Dr. Lowell Crow for informing me about the SNS facilities.

Thanks to Dr. Russell Taylor and his laboratory at the Kansas State University for their support when developing the testing boards for this project. Also thanks to Dr. Douglas McGregor and the National Science foundation for the funding of this project and granting me the opportunity to contribute to their cause.

My most heartfelt thanks goes to my wife Reagan Antonacci. Without her unconditional love and support this could not have been possible. You are a saint. To my children, Jordan, Brandon, and Kaiden for being patient with my dedication to this work and my time spent away from home. I would also like to give a special thanks to my sister-in-law Darcie Schean for her selfless support to my family.

Thanks to my parents Robert Antonacci and Kathy Romita for their support and encouragement throughout my life. You both taught me to aspire and reach for the highest goals. Thanks to rest of my family for always being there and pushing me only upward.

## **ABSTRACT**

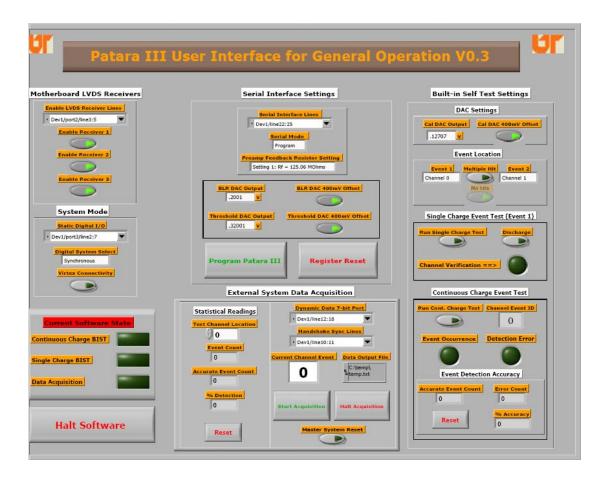

This thesis presents the design of multiple analog and digital blocks required to implement a desired solid-state data acquisition system for the High Efficiency Neutron Detector Array (HENDA) project under the Spallation Neutron Source (SNS) at Oak Ridge National Laboratory (ORNL). This system encloses and is an extension of prior work described in [1] and [2]. The first prototype chip, named *Patara*, contained a charge sensitive front-end amplifier [2], and a semi-Gaussian shaper with baseline restore circuitry [1]. Patara III, described in this thesis, involved the addition of the following system components; two comparators, a selectable synchronous/asynchronous digital backend, priority and binary encoders, nine LVDS drivers/receivers, three 8-bit current driven calibration DAC's, two BGR's, and a 99-bit serial shift register with channel testmode circuitry. The design approach for all major blocks will be discussed along with overall system simulations. In addition, the testing procedure and associated measured results will be summarized illustrating a successful system design. This ASIC was fabricated using the Taiwan Semiconductor Manufacturing Company (TSMC) 0.35-um process available through MOSIS.

# TABLE OF CONTENTS

| CHAPTER I                | INTRODUCTION AND OVERVIEW                                      | 1  |

|--------------------------|----------------------------------------------------------------|----|

|                          | uction                                                         |    |

|                          | ation                                                          |    |

|                          | iew                                                            |    |

|                          | on-based linear thermal neutron detector                       |    |

| 1.3.2 16-c<br>1.3.3 64-c | hannel analog front-end (Patara)                               | 4  |

|                          | hannel data acquisition system (Patara III)                    |    |

|                          |                                                                |    |

| CHAPTER II               | SYSTEM OVERVIEW AND PREVIOUS WORK                              | ð  |

| 2.1 Funda                | umentals of Radiation Detection Systems                        | 8  |

|                          | ous Work                                                       |    |

| 2.2.1 Patar              | ra: Charge Sensitive Preamplifier [2]                          | 11 |

| 2.2.2 Patar              | ra: Semi-Gaussian Shaper and Base-line Restore [1]             | 14 |

|                          | ra Front End Block Diagram                                     |    |

|                          | n Requirements and Block Diagram                               |    |

|                          | Interface Requirements                                         |    |

| 2.3.2 Dete               | ector Readout Channel for Patara III                           | 21 |

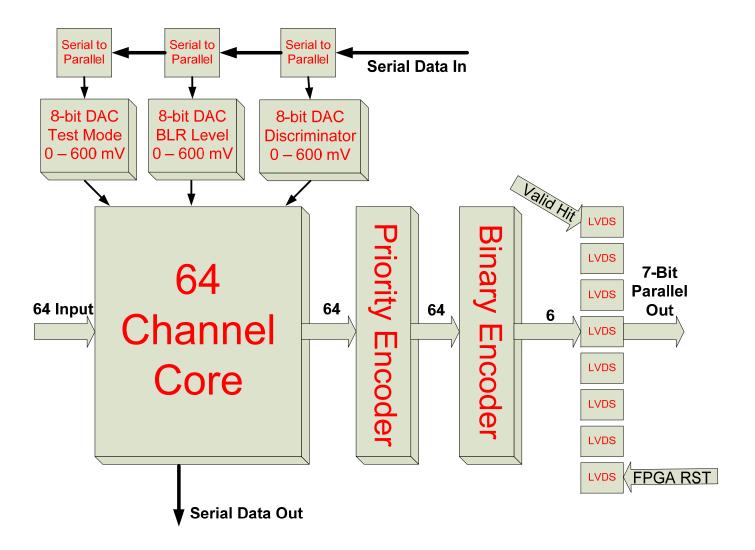

| 2.3.3 64-0               | Channel System Block Diagram for Patara III                    | 23 |

| CHAPTER II  3.1 Analog   | DESIGN OF THE MIXED-SIGNAL COMPONENTS of to Digital Conversion |    |

| 3.1.1 Disc               | rimination Level and Baseline Level Derivation                 |    |

|                          | parator Design and Schematic                                   |    |

|                          | ulation Results and Discussion.                                |    |

|                          | able Synchronous/Asynchronous Digital Backend                  |    |

|                          | chronous Edge Detection Logic and System Registers (System A)  |    |

|                          | em Select Circuitry (System A / System A Prime)                |    |

|                          | em Simulation and Timing Diagram                               |    |

|                          | 64 Priority Encoder                                            |    |

|                          | t Priority Encoder Cell                                        |    |

|                          | llel Priority Look-Ahead Architecture                          |    |

|                          | 6 Binary Encoder                                               |    |

|                          | c 4-to-2 Binary Encoder                                        |    |

|                          | o-6 Binary Encoder Realization                                 |    |

| 3.5 Valid                | Data Flag                                                      | 52 |

|                          | oltage Differential Signaling Driver and Receiver              |    |

|                          | LVDS Standard [20]                                             |    |

|                          | OS Driver Topology and Simulation                              |    |

|                          | OS Receiver Topology and Simulation                            |    |

|                          | e/Disable Bandgap Reference                                    |    |

|                          | R Fundamentals                                                 |    |

| 3.7.2 BGR                | R Topology and Simulation                                      | 62 |

| 3.7         | .3 BGR Programmability and Output Buffering          | 65   |

|-------------|------------------------------------------------------|------|

| 3.8         | 8-Bit Current Driven Digital to Analog Converter     |      |

| 3.8         |                                                      |      |

| 3.8         | .2 Simulation Results                                | 72   |

| 3.9         | 99-Bit Serial Shift Register and Test Mode Circuitry | 75   |

| 3.10        | System Simulation Results                            | 78   |

| СНАР        | TER IV SYSTEM TESTING AND VERIFICATION               | 80   |

| 4.1         | Physical Design                                      | 80   |

| 4.2         | Testing System Design and Configuration              |      |

| 4.2         |                                                      |      |

| 4.2         | $\mathcal{E}^{-1}$                                   |      |

| 4.2         |                                                      |      |

| 4.2         | · · · · · · · · · · · · · · · · · · ·                |      |

| 4.2         |                                                      |      |

| 4.2         | 1                                                    |      |

| 4.3         |                                                      |      |

| 4.3         |                                                      |      |

| 4.3         | $\varepsilon$                                        |      |

| 4.3<br>4.3  |                                                      |      |

| 4.3         | .4 Weastred Results Summary                          | 110  |

| CHAP        | TER V CONCLUSIONS                                    | 111  |

| 5.1         | Conclusion                                           | 111  |

| 5.2         | Future Work                                          | 112  |

|             |                                                      |      |

| LIST C      | OF REFERENCES                                        | 114  |

| APPEN       | DIX                                                  | 117  |

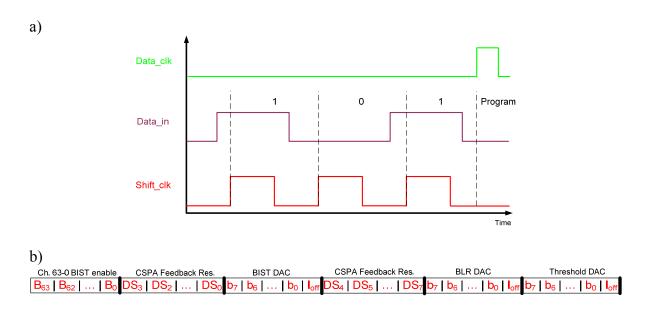

| A.1         | Serial Programming Interface and System Test Mode    | 118  |

| A.1         | .1 Serial Input Specifications                       |      |

|             | .2 BIST Operational Description                      |      |

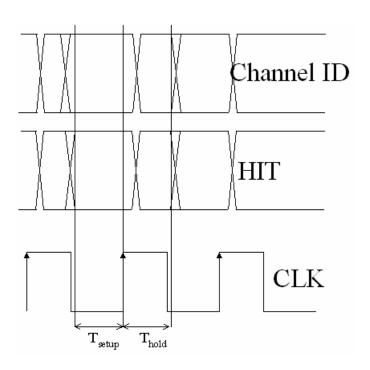

| A.2         | Interfacing the Dynamic Digital Output               | 123  |

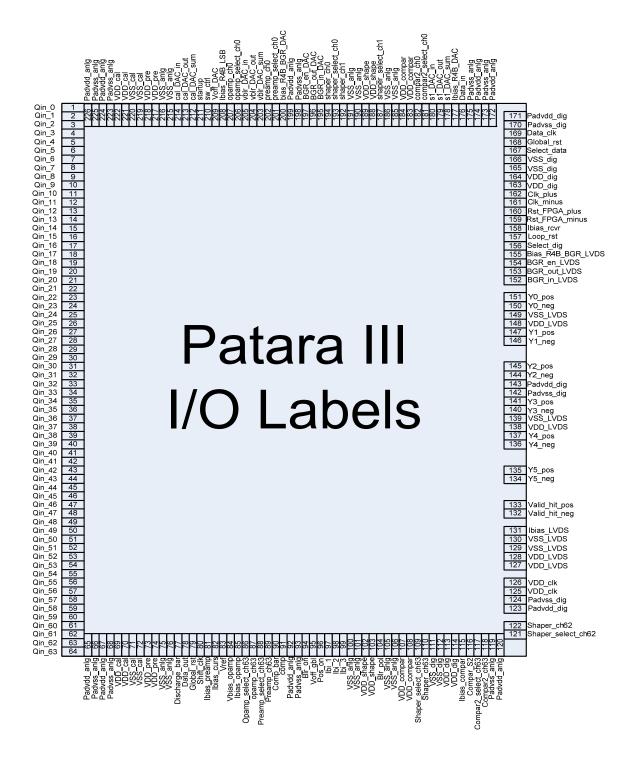

| A.3         | Patara III Pin-Out Diagram and Description           |      |

| <i>B.1</i>  | Motherboard                                          |      |

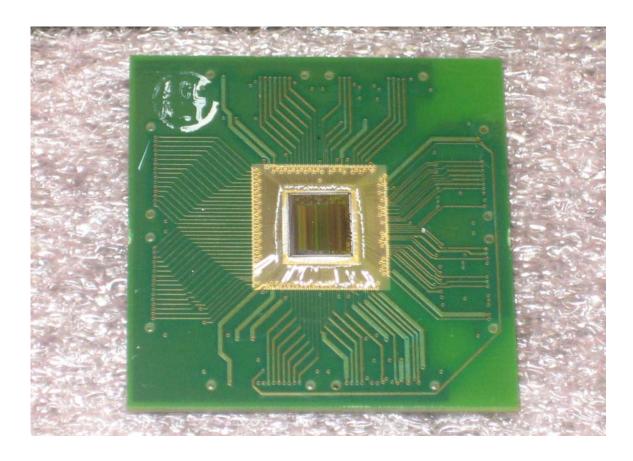

| B.2         | Daughter Card and ASIC                               |      |

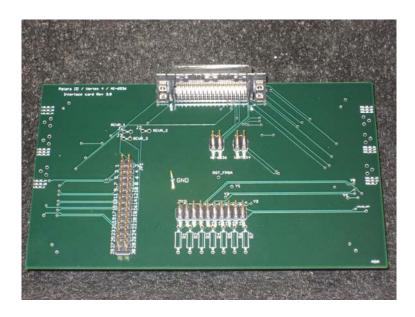

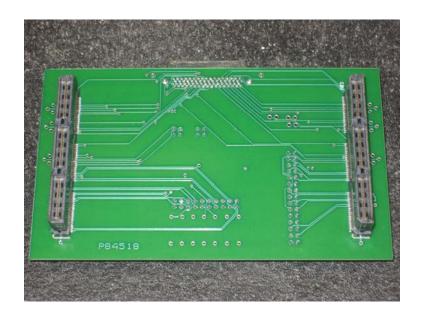

| B.3         | Interface Card and Virtex 4 Board                    |      |

| X 7 T (T) A |                                                      | 4.40 |

# LIST OF TABLES

| Table 2.1 –System Select and Feedback Loop Rest truth table                      | 23  |

|----------------------------------------------------------------------------------|-----|

| Table 3.1 – Digital system interface logic for the rear output card connectivity |     |

| Table 3.2 – ANSI/TIA/EIA-644-A standards for LVDS transmission [20]              | 54  |

| Table 4.1 – General results summary for the Patara III ASIC                      | 110 |

| Table A.1 – Serial interface line description                                    | 118 |

| Table A.2 – Theoretical DAC output voltage with a given input word               | 121 |

| Table A.3 – Patara III pin-out description                                       | 124 |

| Table B.1 – Motherboard dip switch descriptions                                  | 132 |

| Table B.2 – Interface card I/O details and Virtex-4/NI-6536 locations            | 138 |

# LIST OF FIGURES

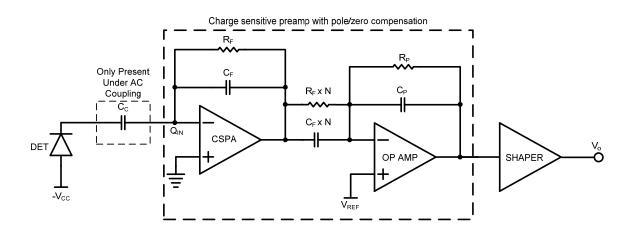

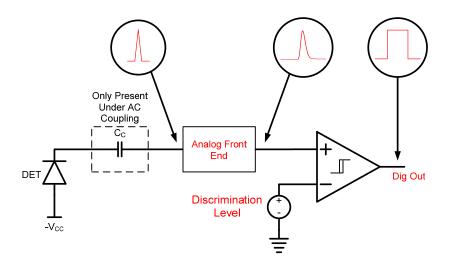

| Figure 2.1 – Typical Radiation System Front End                                              | 8       |

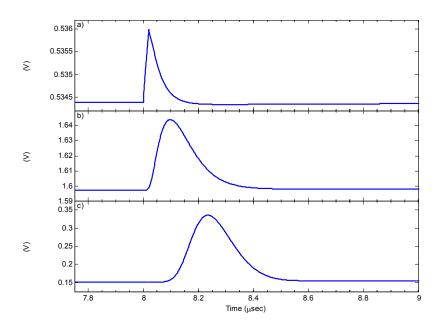

|----------------------------------------------------------------------------------------------|---------|

| Figure $2.2 - a$ ) Example of a detector output, b) The CSPA output after the first real     | ıl pole |

| with the given detector output, c) The shaper output with the given CSPA output              |         |

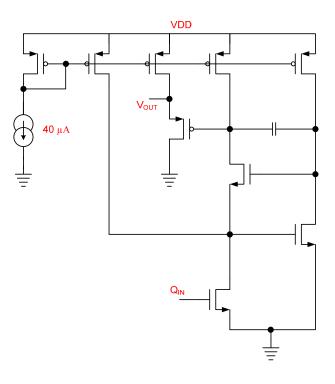

| Figure 2.3 – CSPA topology without feedback [2]                                              |         |

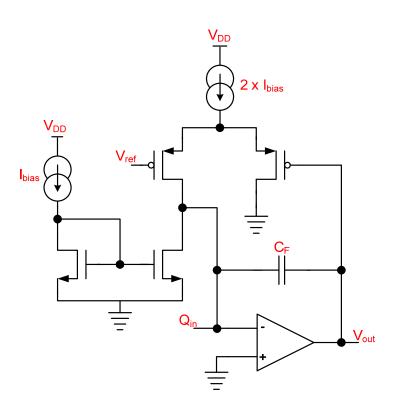

| Figure 2.4 – Active feedback network [2]                                                     |         |

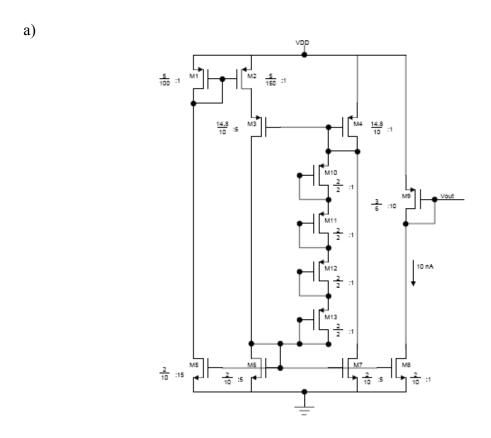

| Figure 2.5 – a) Nanoampere current source for the CSPA feedback network, b)                  |         |

| DAC for bias current scaling [2]                                                             | 15      |

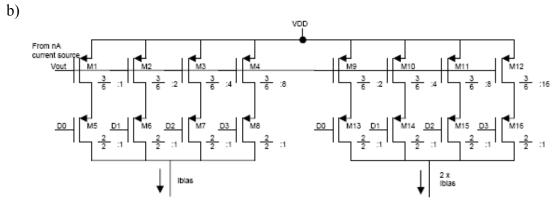

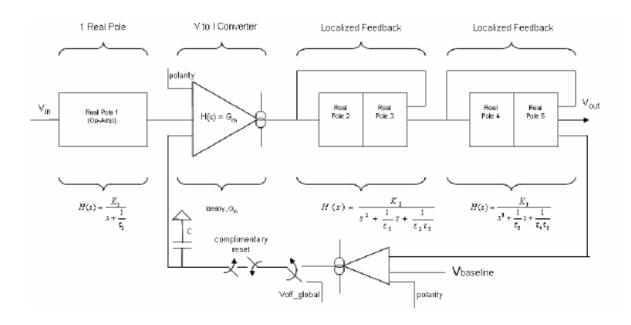

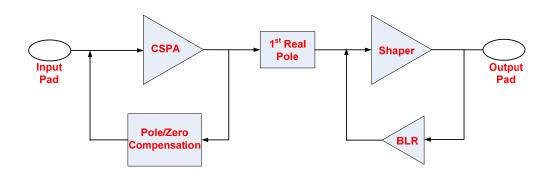

| Figure 2.6 – Conceptual shaper block diagram [1]                                             |         |

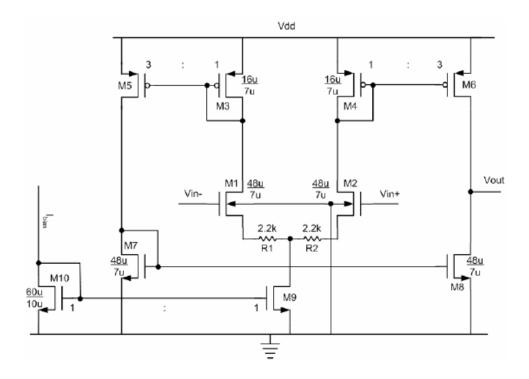

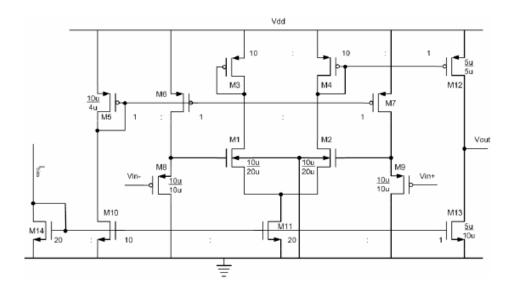

| Figure 2.7 – Operational transconductance amplifier topology [1]                             | 17      |

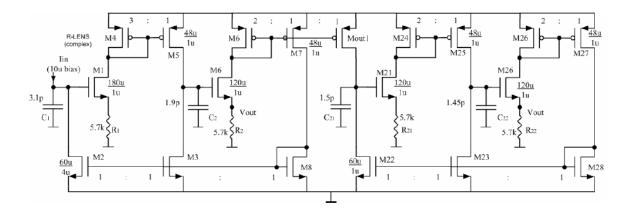

| Figure 2.8 – Four-pole cascade complex conjugate R-Lens filter topology [1]                  |         |

| Figure 2.9 – Ground sensing baseline restore operational transconductance amplifi            |         |

|                                                                                              |         |

| Figure 2.10 – Patara Channel Block Diagram                                                   |         |

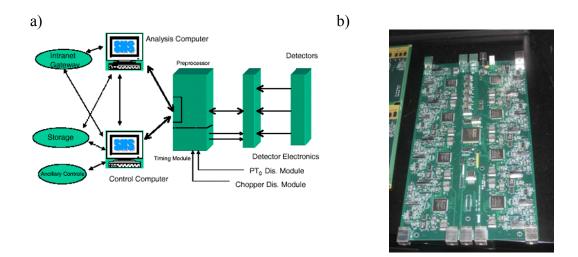

| Figure 2.11 – a) Example of an SNS system [6], b) example of a rear output card (            | ROC)    |

|                                                                                              |         |

| Figure 2.12 – Readout channel block diagram                                                  | 22      |

| Figure 2.13 – Patara III ASIC block level overview                                           |         |

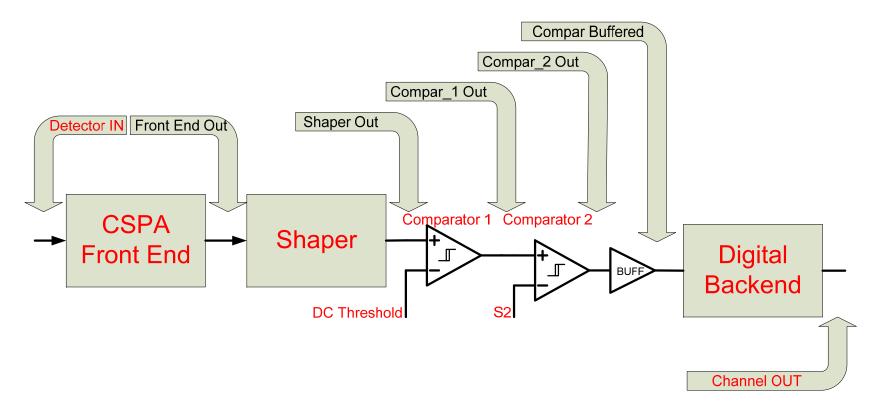

| Figure 3.1 – Signal processing channel with comparator and example waveforms                 |         |

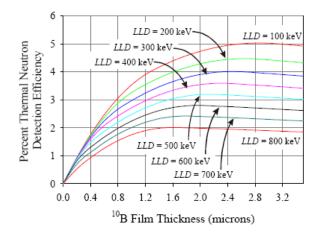

| Figure 3.2 – Thermal neutron efficiency as a function of <sup>10</sup> B thickness and LLD s | etting  |

| from [12]                                                                                    |         |

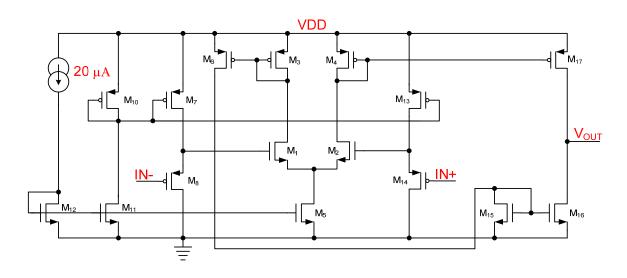

| Figure 3.3 – Ground sensing comparator used for DC level discrimination                      | 30      |

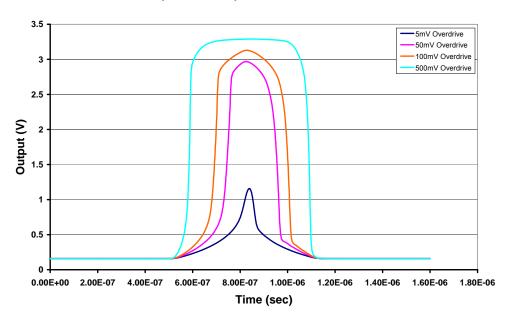

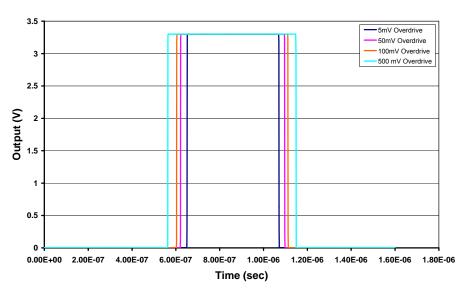

| Figure 3.4 – Comparator output characteristics at different input overdrives                 | 32      |

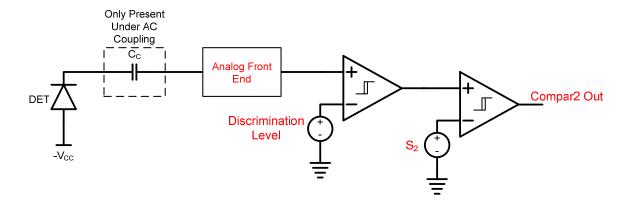

| Figure 3.5 – Channel block diagram with sequential comparator configuration                  |         |

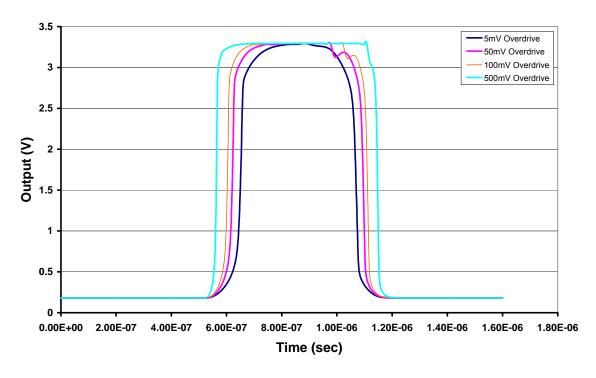

| Figure 3.6 – Comparator 2 output at varying input overdrives to the first comparator         | · 33    |

| Figure 3.7 – Digitally buffered sequential comparator with different input overdrives        | s 34    |

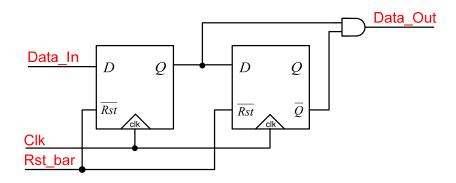

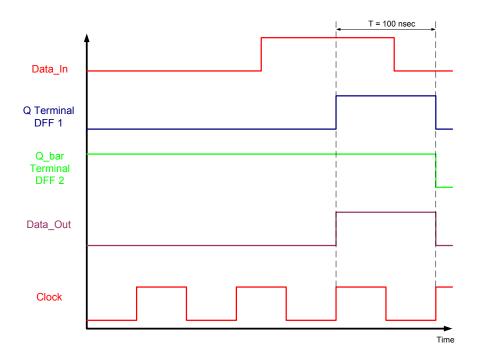

| Figure 3.8 – Synchronous edge detection logic [14]                                           | 35      |

| Figure 3.9 – Timing diagram for the synchronous edge detection circuitry                     | 36      |

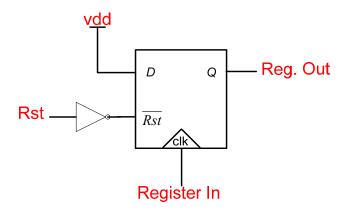

| Figure 3.10 – DFF register configuration                                                     |         |

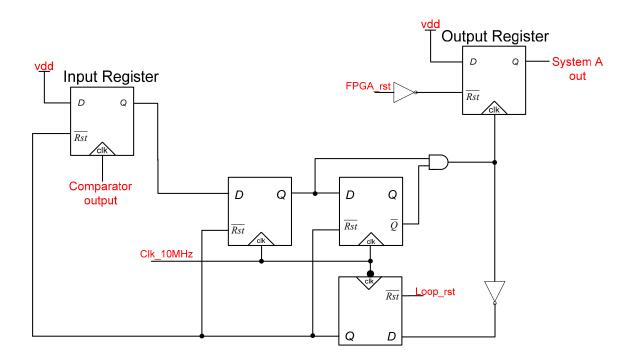

| Figure 3.11 – System A with input and output registers                                       |         |

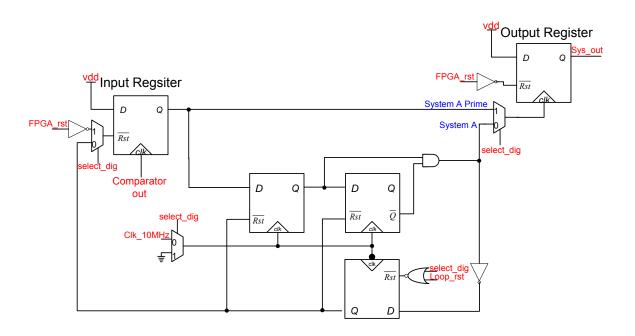

| Figure 3.12 - System A and System A Prime schematic along with input and of                  |         |

| registers                                                                                    | 39      |

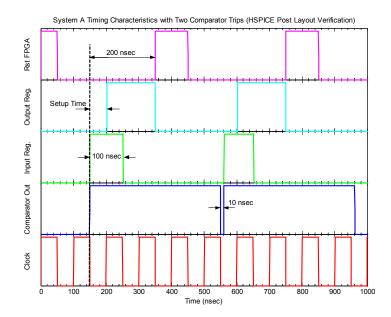

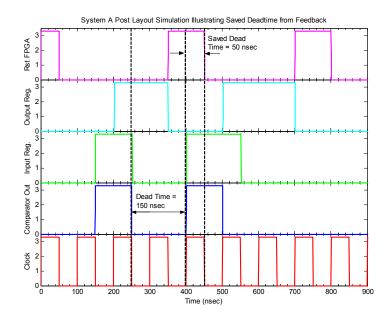

| Figure 3.13 – System A post layout simulation results illustrating timing characterist       | ics 41  |

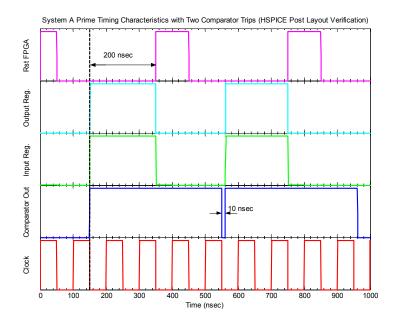

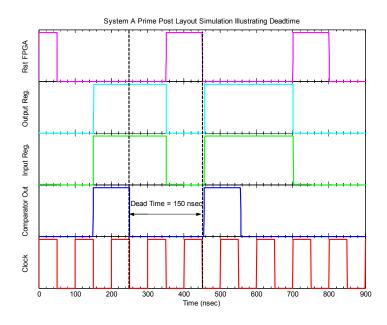

| Figure 3.14 - System A Prime post layout simulation results illustrating t                   | iming   |

| characteristics                                                                              |         |

| Figure 3.15 – System A simulation results illustrating system "dead time"                    | 42      |

| Figure 3.16 – System A Prime simulation result illustrating system "dead time"               | 42      |

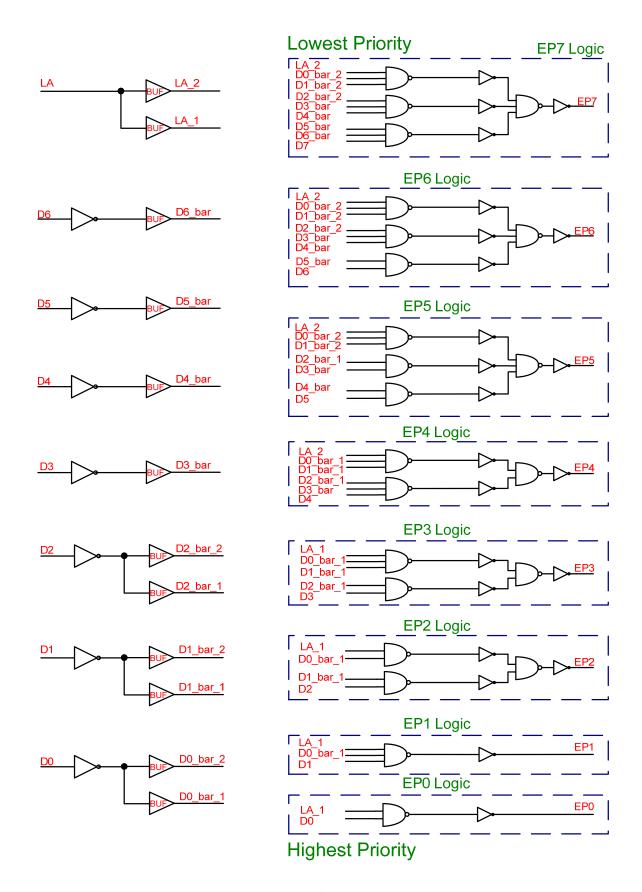

| Figure 3.17 – 8-Bit Priority Encoder Cell.                                                   | 46      |

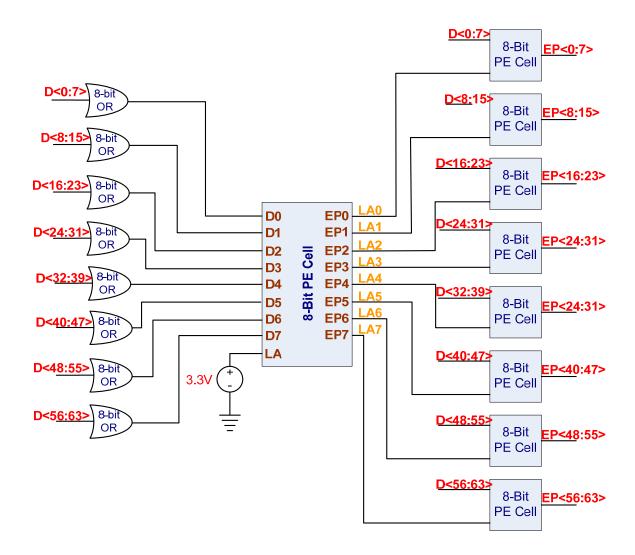

| Figure 3.18 – 64-bit parallel priority look-head encoder                                     | 48      |

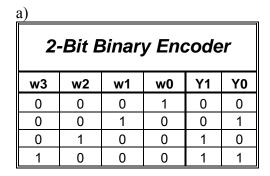

| Figure 3.19 – a) truth table and b) logic realization for a 2-bit (4-to-2) binary encode     |         |

|                                                                                              | 49      |

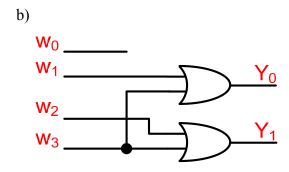

| Figure 3.20 – 32-input OR gate fan-in.                                                       |         |

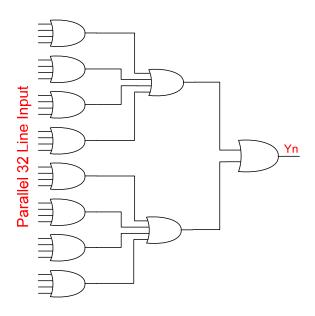

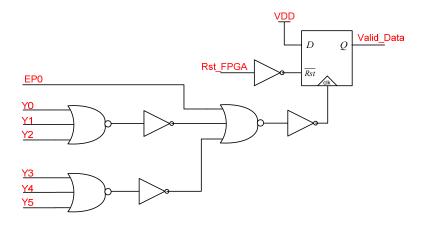

| Figure 3.21 – Valid data flag circuitry along with output registering                        | 52      |

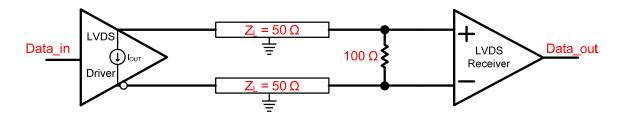

| Figure 3.22 – LVDS point-to-point interface with transmission lines and term                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ination  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53       |

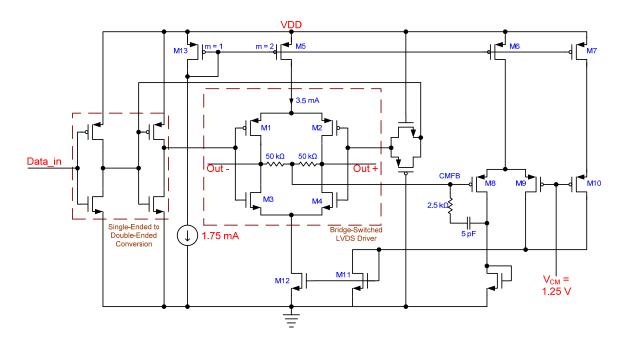

| Figure 3.23 – Bridge-switched based LVDS driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55       |

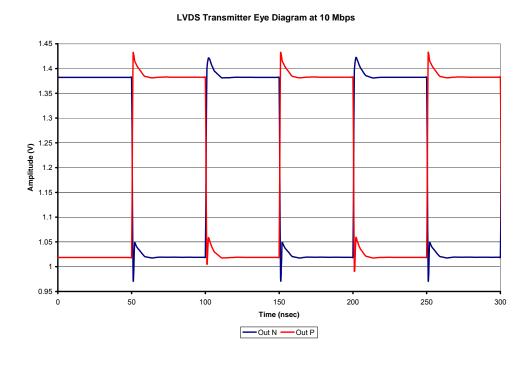

| Figure 3.24 – Simulated LVDS transmitter eye diagram at a data rate of 10 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56       |

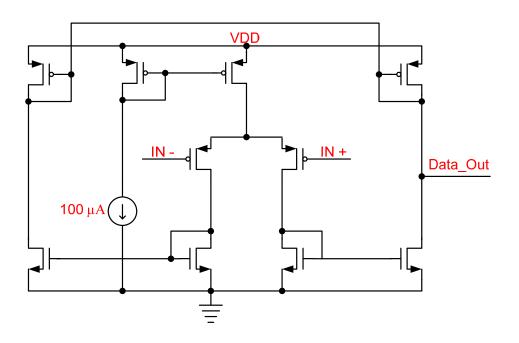

| Figure 3.25 – LVDS receiver topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

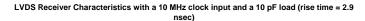

| Figure 3.26 - SimulatedLVDS receiver output with a 10 MHz clock input and a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 10 pF  |

| load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58       |

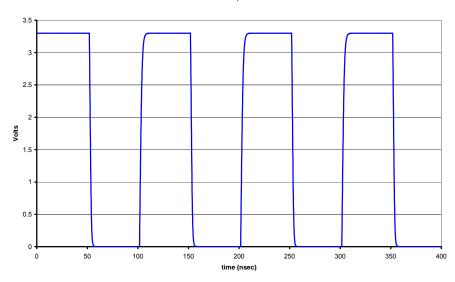

| Figure 3.27 - Simulated LVDS receiver transfer characteristic illustrating difference of the control of the con | erential |

| input threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58       |

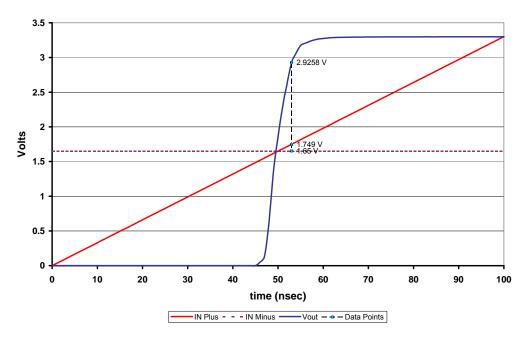

| Figure 3.28 – Thermal voltage current reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60       |

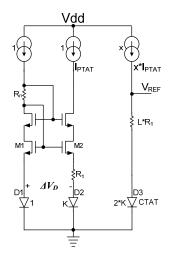

| Figure 3.29 – Basic BGR topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62       |

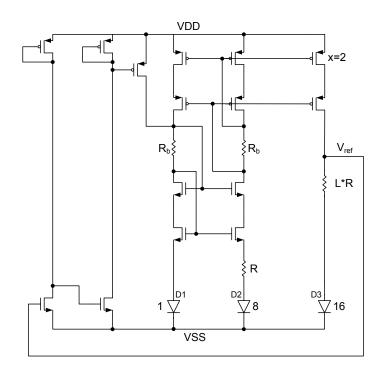

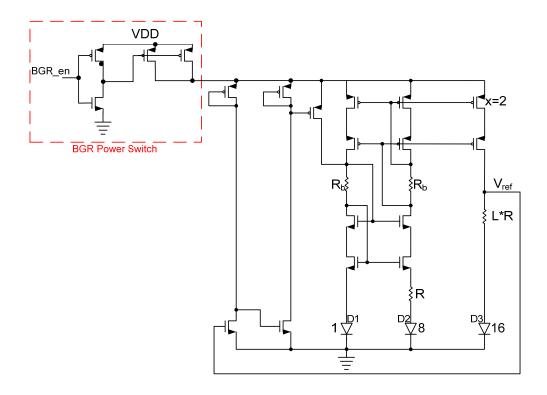

| Figure 3.30 – On chip bandgap voltage reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63       |

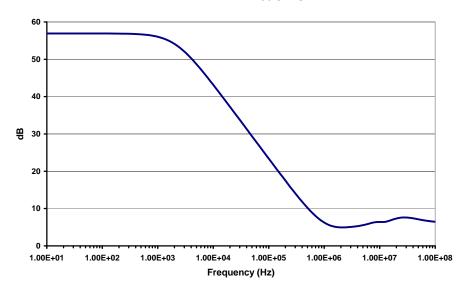

| Figure 3.31 – BGR simulated PSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64       |

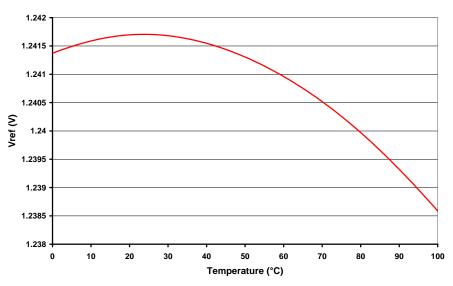

| Figure 3.32 – BGR simulated temperature characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64       |

| Figure 3.33 – Bandgap reference with programmable switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65       |

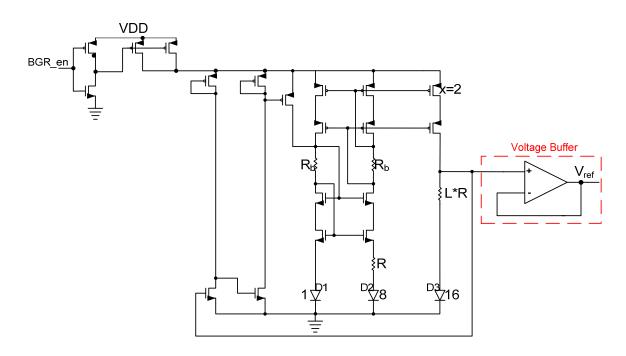

| Figure 3.34 – Bandgap reference with voltage buffering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66       |

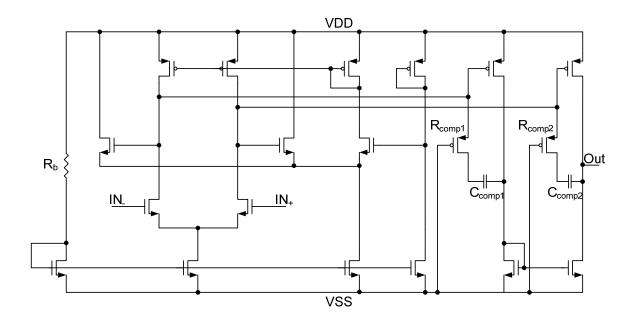

| Figure 3.35 – RHIC4B op amp used for voltage buffering [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67       |

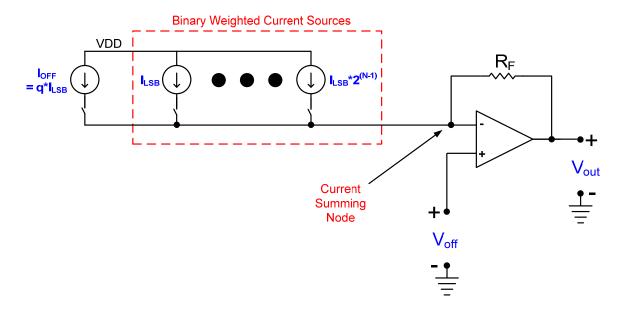

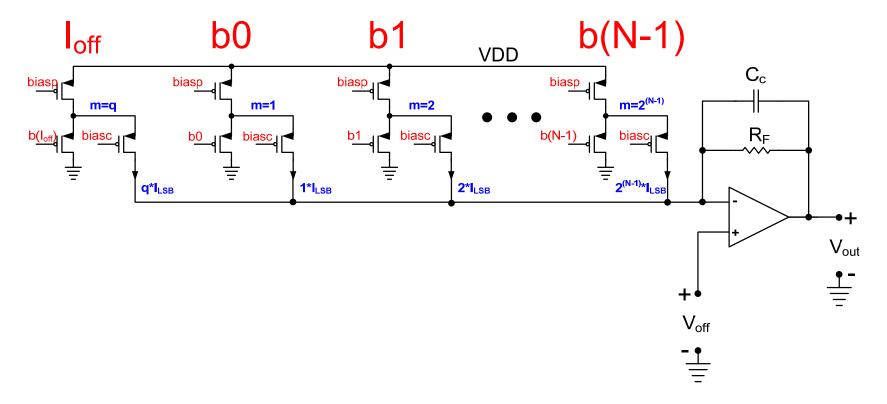

| Figure 3.36 – Current driven DAC architecture overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69       |

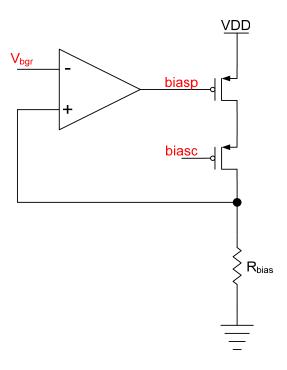

| Figure 3.37 – 16x LSB bias circuit for the binary weighted current mirror bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70       |

| Figure 3.38 – Current driven DAC architecture without 16× LSB bias circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73       |

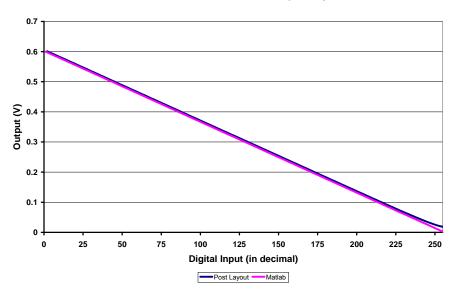

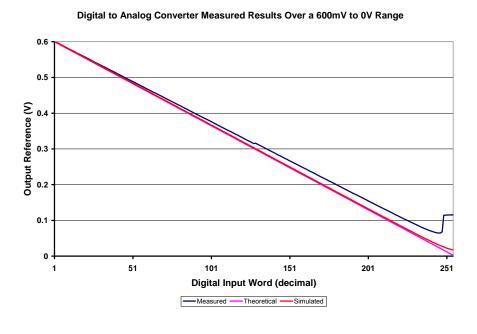

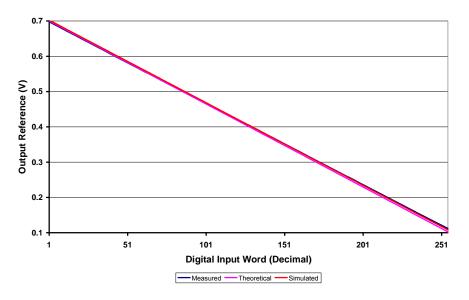

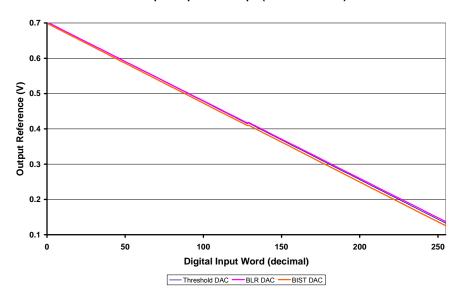

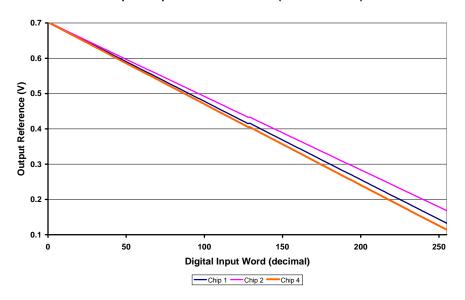

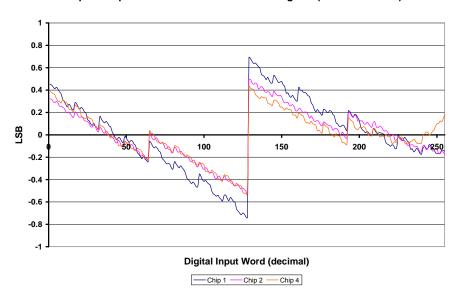

| Figure 3.39 – Simulated 8-bit DAC transfer curve post layout and Matlab curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 74       |

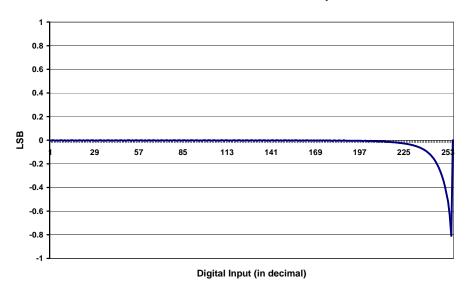

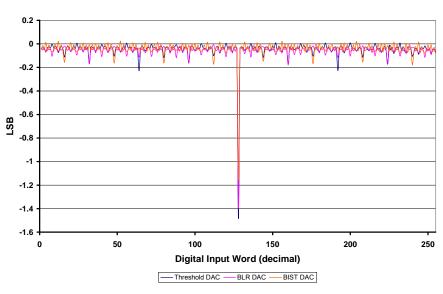

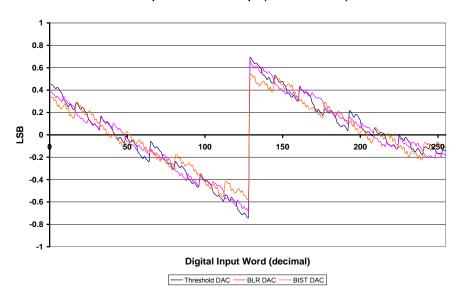

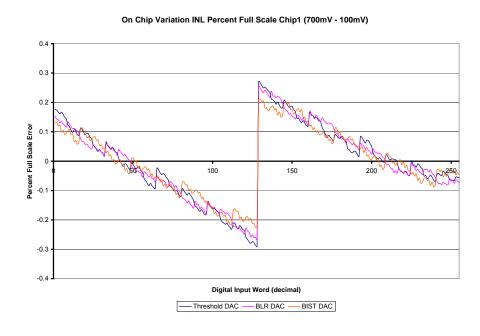

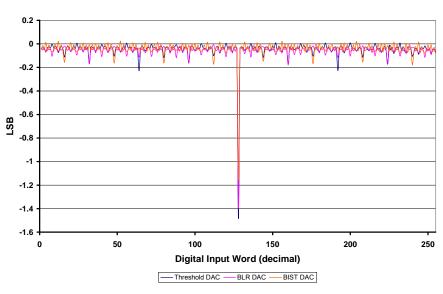

| Figure 3.40 – Simulated 8-bit DAC DNL plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

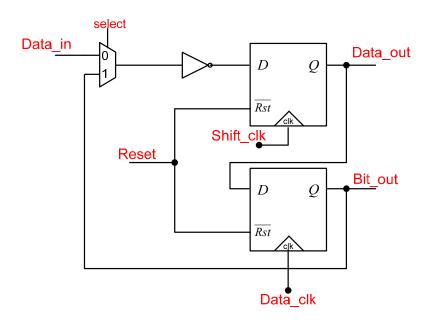

| Figure 3.41 – Serial shift register 1-bit cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

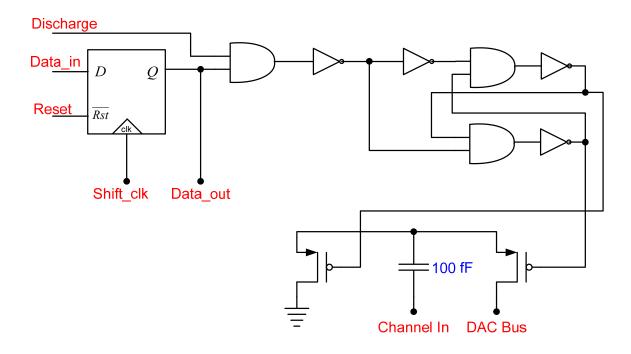

| Figure 3.42 – Built in self test circuitry cell with serial register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

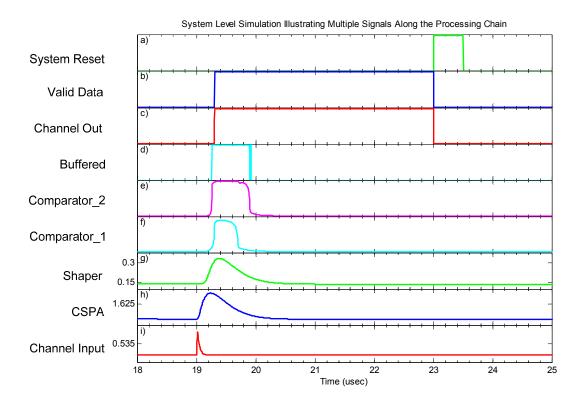

| Figure $3.43 - a$ ) System reset provided by the ROC, b) valid data flag provided                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| ASIC, c) channel 0 register output from the 64-channel core, d) digital by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | uffered  |

| output e) comparator 2 output, f) comparator 1 output, g) Shaper output, h) I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| Output after first real pole, i) detector input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79       |

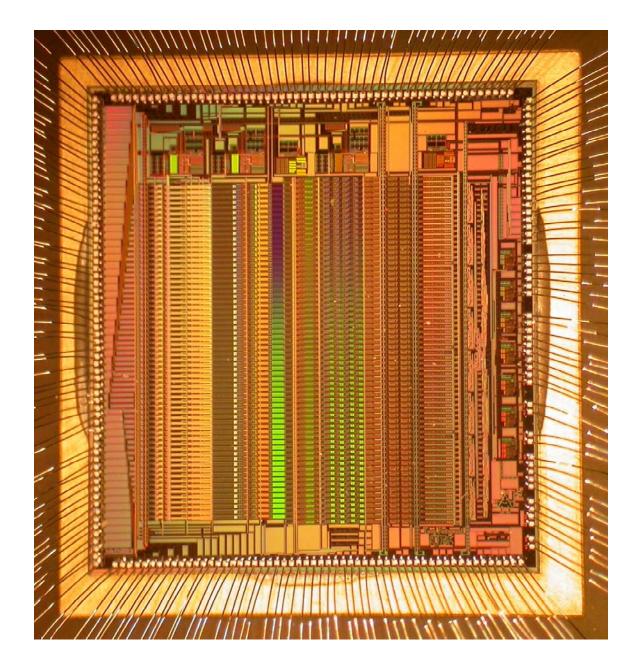

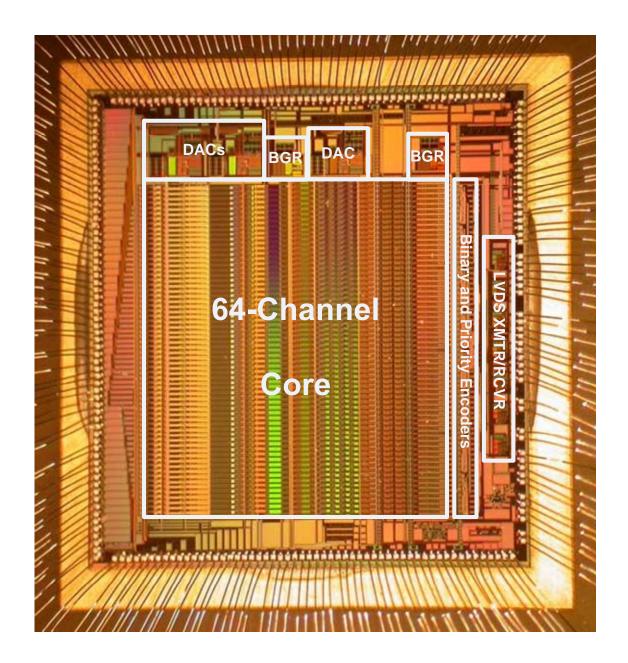

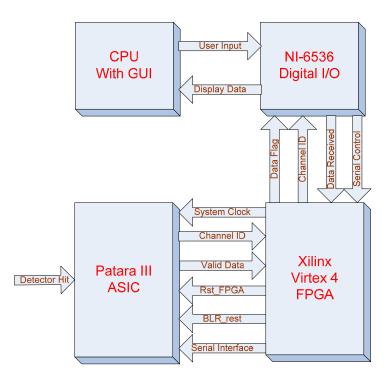

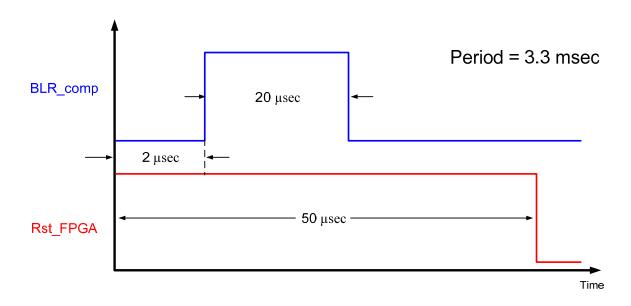

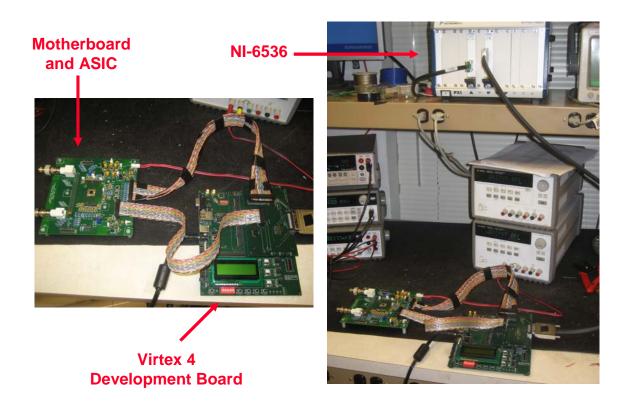

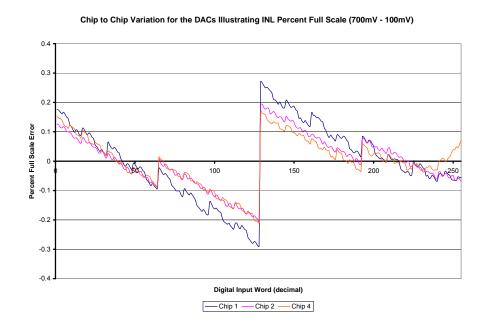

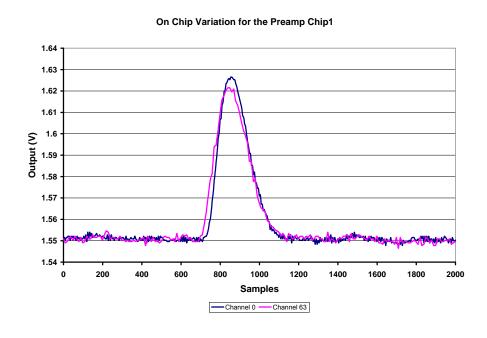

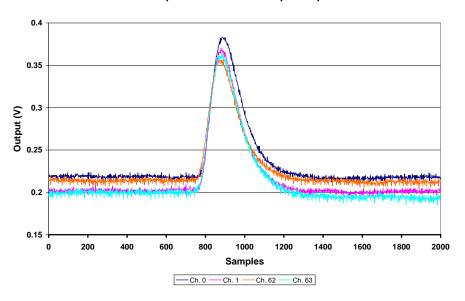

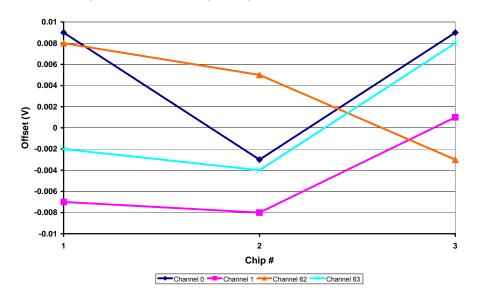

| Figure 4.1 – Patara III ASIC micrograph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81       |